Samco was the first Japanese semiconductor process equipment manufacturer to provide Silicon Deep Reactive Ion Etching (DRIE) systems using the Bosch Process. We offer DRIE systems with a range of sample sizes and number of chambers for MEMS device fabrication and TSV via-hole etching. Our systems have industry-leading process capabilities, and the product lineup covers both R&D and production. For high-volume device manufacturing, a double reaction chamber specification is also available.

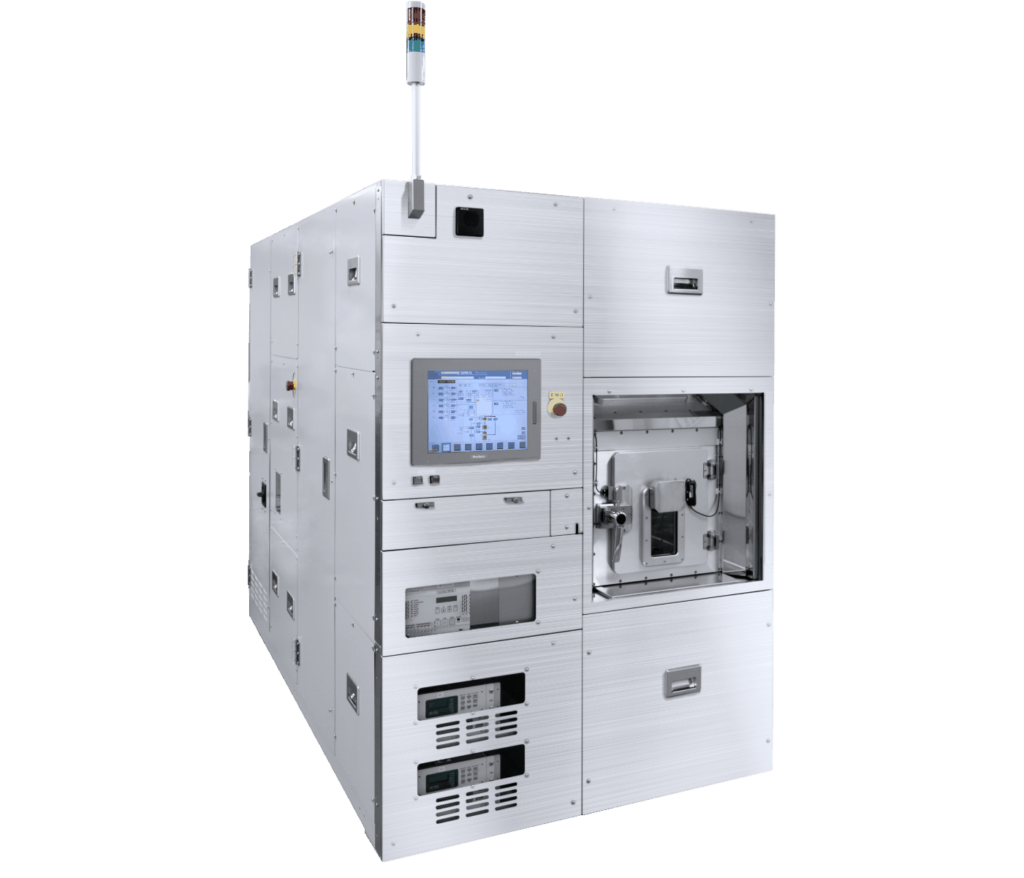

DRIE System Lineup

Key Features & Benefits

- Industry leading etch rates of over 50 μm/min

- High selectivity of over 250:1 (Si:Photoresist)

- Uniformity of ±5% or better (ø4, 6, and 8″ wafers)

- High aspect ratio (greater than 100:1)

- Low scalloping, smooth sidewall profile (less than 0.1 μm scallops)

- Patented, dual frequency silion on insulator (SOI) anti-notch etching technique

- Unique “anti-tilt” feature that ensures high uniformity

- Electrostatic chuck and helium backside cooling (for wafer temperature control)

- ICP source can be modified for etching of SiO2